Computer microarchitecture is a fascination of mine, and I believe everyone ought to be awed by it to some degree. The incalculatble intricacy and ingenious engineering which goes into the countless chip designs integrated within everything we use is staggering. It is remarkable how mundane such pieces of silicon have become in our daily lives despite the countless hours of invention required for them to exist in the first place.

That is why I took it upon myself to learn about every layer of the machines we rely on from hardware description language-level on-up. In my career, I hope to be involved in the design of ASICs in some way.

32-bit MIPS Processor with Instruction Cache

RISC-V Processors on FPGA

FFT Audio Bluetooth Speaker - FPGA-Based Version

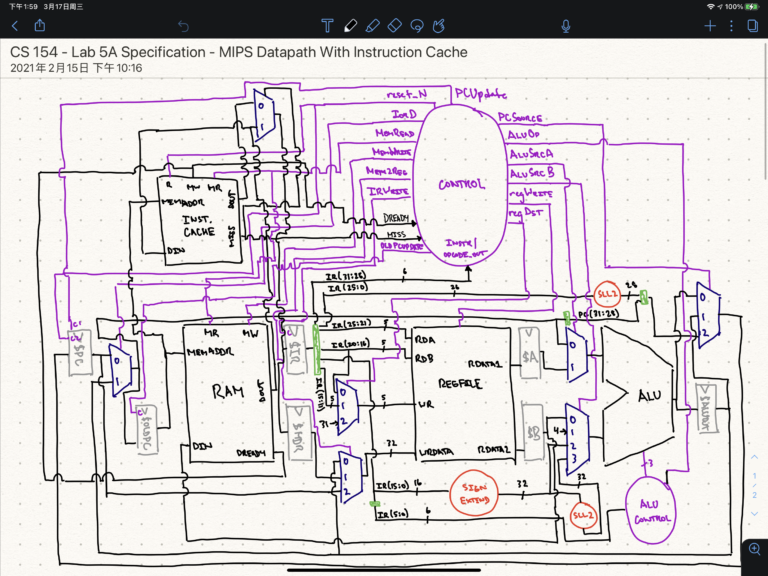

32-bit MIPS Processor with Instruction Cache

As part of my computer architecture studies, I designed a 32-bit MIPS processor with instruction cache from the ground up in VHDL. It is functional in simulation.

This was my first major foray into digital logic design, and it hooked my interest in computer architecture and other HDL projects.

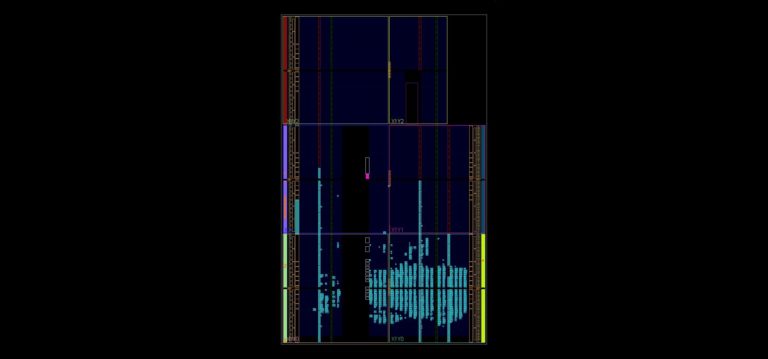

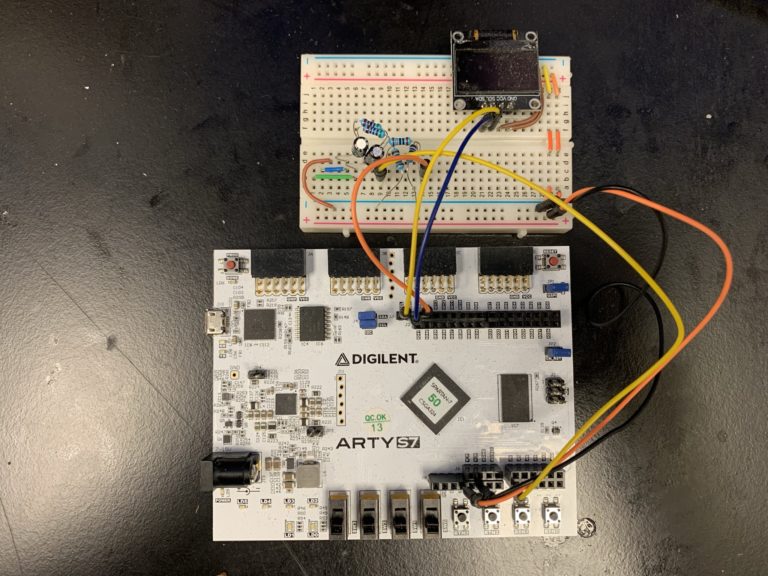

RISC-V Processors on FPGA

After writing a simulation-viable MIPS processor of my own, I wanted to see what others had done. I downloaded, adapted, synthesized, and implemented two different RISC-V designs on a Diligent Arty S7 FPGA board:

- Potato Processor – FPGA-usable RISC-V (RV32I) processor design

- NEORV32 Processor – A configurable RISC-V 32-bit processor design and SoC optimized for microcontrollers

FFT Audio Bluetooth Speaker - FPGA-Based Version

This project originally started as an attempt to understand discrete fast Fourier transforms (DFFTs) by applying it in an audio processing project centered around a SAMD21 microcontroller. Then, I aimed to use Verilog to implement the DFFT algorithm on an FPGA for my first attempt at applied digital logic design and hardware-accelerated computing. Pretty soon, the project took on a life of its own with future plans as a full-blown Bluetooth speaker with audio visualization features.

Take a look at the GitHub writeups/documentation of both versions of my project here: